However, this application is limited to rather small signal voltage excursions around the drain-source voltage VDS=0 (app. With reference to the first formula in your contribution - this is the equation which shows how a FET can be used as a variable resistor, controlled by the gate-source voltagwe VGS. I am afraid that you are mixing two different things. You can re-derive the polynomial, with a linear resistor added onto the exponential base-emitter diode non-linearity, and have the revised math for this.

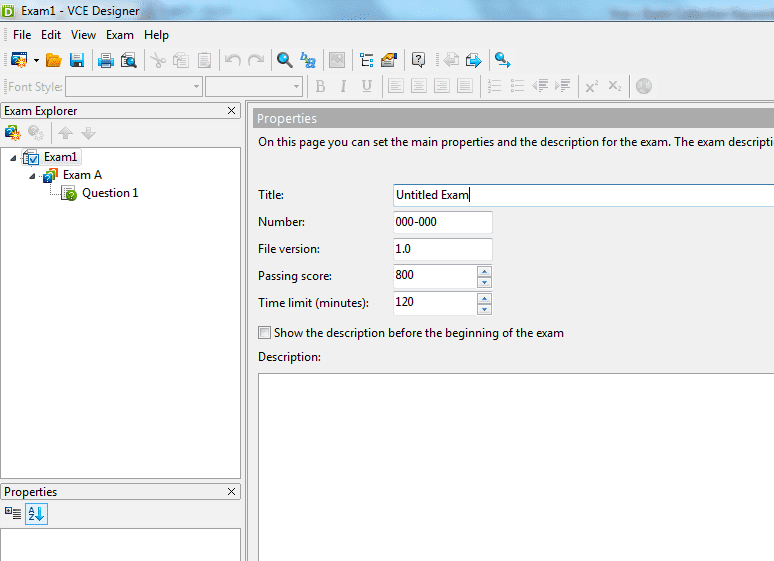

VCE DESIGNER 3.1.1 SERIES

NOW THE KEY IDEA: if you have a resistor in series with the emitter, and there is NO CAPACITOR across that resistor, you can dial up the desired amount of distortion.Ī resistor with DC drop of 10 * 0.026 volts, will greatly reduce the distortion.Ī resistor with DC drop of 100 * 0.026 volts, produces even less distortion.

The 3rd order term predicts A * A * A (self) distortion, as well as predicting A * A * B and A * B * B (which you will find are symmetric effects).Įxamine the 3rd Order Intercept as useful. Examine the 2nd Order Intercept as useful. The 2nd order term predicts A * B intermodulation distortion, as well as predicting A * A (self) distortion. Ĭan be very useful to people evaluating low distortion audio circuits or low distortion ADC preamplifiers or low distortion Radio Frequency amplifiers, or high distortion guitar amplifiers.

New resistor in series RC: R_gain_set = 510 ohms (green/brown/brown)Īnd that new capacitor ithe series RC C_low_corner = 22uf Now add a series RC in parallel with the emitter resistor, and make that new resistor be r/10 you'll have a rather linear gain = 10x. Set r2 = r/2, and you'll have a large and nearly linear output range, with gain of -1. Biased like that, the transistor is in saturation, and will not amplify.

0 kommentar(er)

0 kommentar(er)